# **Product Specification**

## XENPAK-SFP+ 10G Adapter

## Features ,,,,

- Compatible with XENPAK MSA Rev.2.0b

- Case Temperature Range:

- Standard: 0°C +70°C

- Duplex SC connector

- Hot pluggable 70 pin connector with XAUI electrical interface

- Management and control via MDIO 2 wire interface

- Complaint with the EU RoHS 6 Environmental Requirements

### ,,,,,2,, Applications ,,,,

10G Ethernet

## Product Description ,,,,

The XENPAK-SFP+ a 10 Gigabit Ethernet XENPAK port into a 10 Gigabit Ethernet SFP+ port. With the converter module, customers have the flexibility to use the 10 Gigabit X2 interface port of a switch with X2 modules or SFP+ modules. This flexibility is critical when the specific type of interface is not available in one or the other form factor or when customers want to use the same form factor for interfaces across multiple platforms deployed in their network. It is a highly integrated, serial optical transponder module for high speed, 10Gbit/s data transmission applications. The module is fully compliant to IEEE 802.3ae standard for Ethernet, making it ideally suited for 10GbE datacom (rack to rack, client interconnection) applications. The transponder operates within a wide case temperature range of 0°C to +70°C and offers optimum heat dissipation and excellent electromagnetic shielding which enables high port densities for 10GbE systems. A 70 pin electrical connector and a duplex SC connector optical interface assure that connectivity is compliant to the X2 and XENPAK MSA.

### A. SFP+ transceiver modules that can be plugged into the Converter Module

| Product Name | Product Description     |

|--------------|-------------------------|

| SR           | 850nm MM 10G SFP+       |

| LR           | 1310nm SM 10G SFP+ 10KM |

| ER           | 1550nm SM 10G SFP+ 40KM |

| ZR           | 1550nm SM 10G SFP+ 70KM |

| CWDM         | CWDM SFP8 10G           |

| DWDM         | CWDM SFP+ 10G           |

## Recommended Operating Conditions

| Feature                                              | Standard                                                               | Performance                                                                                                                                                                                                 |

|------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrostatic Discharge (ESD) to the Electrical Pins | MIL STD 883G Method<br>3015.7                                          | Class 1C (>1000V)                                                                                                                                                                                           |

| Electrostatic Discharge to the Enclosure             | EN 55024:1998+A1+A2<br>IEC61000 4 2<br>GR 1089 CORE                    | Compliant with standards                                                                                                                                                                                    |

| Electromagnetic<br>Interference (EMI)                | FCC Part 15 Class B<br>EN55022:2006<br>CISPR 22B :2006<br>VCCI Class B | Compliant with standards Noise frequency range: 30MHz to 6GHz. Good system EMI design practice required to achieve Class B margins. System margins are dependent on customer host board and chassis design. |

| Immunity                                             | EN 55024:1998+A1+A2<br>IEC 61000 4 3                                   | Compliant with standards.  1KHz sine wave, 80% AM, from 80MHz to 1GHz. No effect on transmitter/receiver performance is detectable between these limits.                                                    |

| RoHS6                                                | RoHS6<br>2002/95/EC 4.1&4.2<br>2005/747/EC 5&7&13                      | Compliant with standards [1]                                                                                                                                                                                |

#### Notes:

[1] For update of the equipments and strict control of raw materials, A-Gear has the ability to supply the customized products since Jan 1, 2007, which meet the requirements of RoHS6 (Restrictions on use of certain Hazardous Substances) of European Union.

In light of item 5 in RoHS exemption list of RoHS Directive 2002/95/EC, Item 5: Lead in glass of cathode ray tubes, electronic components and fluorescent tubes. In light of item 13 in RoHS exemption list of RoHS Directive

## **U**-**り**と**U** ■ A-GEAR World Wide Manufacturing

2005/747/EC, Item13: Lead and cadmium in optical and filter glass. The three exemptions are being concerned for A-Gear's transceivers, because A-Gear's transceivers use glass, which may contain Pb, for components such as lenses, windows, isolators, and other electronic components.

## ,,,,,6,, Electro Static Discharge (ESD)

The maximum electrostatic charge based on a human body model and the conditions as outlined below is:

| Parameter | Symbol    | Min.    | Typical | Max. | Unit    |

|-----------|-----------|---------|---------|------|---------|

| Static    | Discharge | Voltage | MIL     | STD  | 883 [1] |

#### **Notes:**

[1] Method

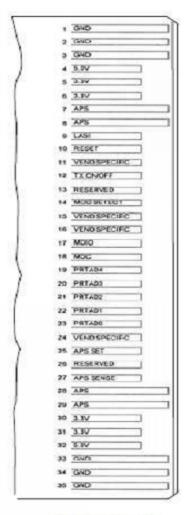

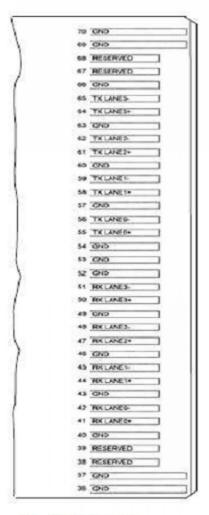

## Electrical Pin Definition

Top view -Top side

Top view-Bottom row

| Pin                                                                                                        | Logic                                   | Symbol     | Name/Description                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5, 6,<br>30, 31                                                                                            | _                                       | 3.3V       | Power Supply of Optical Receiver and Transmitter and Control Circuits [2]                                                                                                     |

| 4, 32                                                                                                      |                                         | 5.0V       | Power Supply of Optical Receiver Frontend [2]                                                                                                                                 |

| 7, 8,<br>28, 29                                                                                            |                                         | APS        | Adaptive Power Supply, Supply of PHY XS and PCS Layer Devices [2]                                                                                                             |

| 27                                                                                                         |                                         | APS SENSE  | APS Sense Output for APS Control Circuit                                                                                                                                      |

| 25                                                                                                         |                                         | APS SET    | Feedback Input for APS, Input of APS Setting Resistor                                                                                                                         |

| 1, 2, 3,<br>33, 34,<br>35, 36,<br>37, 40,<br>43, 46,<br>49, 52,<br>53, 54,<br>57, 60,<br>63, 66,<br>69, 70 |                                         | GND        | Common Electrical Ground [1]                                                                                                                                                  |

| 9                                                                                                          | 1.2V<br>CMOS<br>Open<br>Drain<br>Output | LASI       | Link Alarm Status Interrupt, low active, Open Drain Output Supposed to operate with 10KL 22KL pull upon host. Logic High: Normal Operation Logic Low: Link Alarm is indicated |

| 18                                                                                                         | Output                                  | MDC        | Management Clock Input [3]                                                                                                                                                    |

| 17                                                                                                         |                                         | MDIO       | Management Data [3]                                                                                                                                                           |

| 14                                                                                                         |                                         | MOD DETECT | 1kL to Ground for APS Circuit Environment                                                                                                                                     |

| 23                                                                                                         | 1.2V<br>CMOS<br>Input                   | PRTADO     | Port Address Bit 0 (Low = 0), internally pulled up by 18kL                                                                                                                    |

| 22                                                                                                         | 1.2V<br>CMOS<br>Input                   | PRTAD1     | Port Address Bit 1 (Low = 0), internally pulled up by 18kL                                                                                                                    |

| 21                                                                                                         | 1.2V<br>CMOS<br>Input                   | PRTAD2     | Port Address Bit 2 (Low = 0), internally pulled up by 18kL                                                                                                                    |

| 20                                                                                                         | 1.2V<br>CMOS<br>Input                   | PRTAD3     | Port Address Bit 3 (Low = 0), internally pulled up by 18kL                                                                                                                    |

| 19                                                                                                         | 1.2V<br>CMOS<br>Input                   | PRTAD4     | Port Address Bit 4 (Low = 0), internally pulled up by 18kL                                                                                                                    |

|                                                                                                            |                                         |            |                                                                                                                                                                               |

| Pin                      | Logic                 | Symbol       | Nama/Description                                                                                                                                                                                   |

|--------------------------|-----------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | Logic                 | Symbol       | Name/Description                                                                                                                                                                                   |

| 13, 38,<br>39, 67,<br>68 |                       | RESERVED     | Reserved by MSA, internally not connected                                                                                                                                                          |

| 26                       |                       | RESERVED     | Reserved for Avalanche Photodiode use, internally not connected [5]                                                                                                                                |

| 10                       | 1.2V<br>CMOS<br>Input | RESET        | Low active Reset Input 10KL pull up on Transceiver Logic high = Normal Operation Logic Low = Reset asserted                                                                                        |

| 12                       | 1.2V<br>CMOS<br>Input | TX ON/OFF    | High active Transmitter Enable Input 10KL pull up on Transceiver Logic high = Transmitter active (normal Operation) And Register Bit 1.9.0 set to low as well Logic Low = shut down of Transmitter |

| 11, 15,<br>16, 24        |                       | VENDSPECIFIC | Vendor Specific Pin,. for proper operation leave unconnected [5]                                                                                                                                   |

| 41                       |                       | RX LANE0+    | Module XAUI Output Lane 0+ [4]                                                                                                                                                                     |

| 42                       |                       | RX LANE0     | Module XAUI Output Lane 0 [4]                                                                                                                                                                      |

| 44                       |                       | RXLANE1+     | Module XAUI Output Lane 1+ [4]                                                                                                                                                                     |

| 45                       |                       | RX LANE 1 -  | Module XAUI Output Lane 1 - [4]                                                                                                                                                                    |

| 47                       |                       | RXLANE2+     | Module XAUI Output Lane 2+ [4]                                                                                                                                                                     |

| 48                       |                       | RXLANE2-     | Module XAUI Output Lane 2 [4]                                                                                                                                                                      |

| 50                       |                       | RXLANE3+     | Module XAUI Output Lane 3+ [4]                                                                                                                                                                     |

| 51                       |                       | RXLANE3-     | Module XAUI Output Lane 3 [4]                                                                                                                                                                      |

| 55                       |                       | TXLANE0+     | Module XAUI Input Lane 0+ [4]                                                                                                                                                                      |

| 56                       |                       | TXLANE0-     | Module XAUI Input Lane 0 [4]                                                                                                                                                                       |

| 58                       |                       | TX LANE1+    | Module XAUI Input Lane 1+ [4]                                                                                                                                                                      |

| 59                       |                       | TXLANE1-     | Module XAUI Input Lane 1 [4]                                                                                                                                                                       |

| 61                       |                       | TXLANE2+     | Module XAUI Input Lane 2+ [4]                                                                                                                                                                      |

| 62                       |                       | TX LANE2-    | Module XAUI Input Lane 2 [4]                                                                                                                                                                       |

| 64                       |                       | TXLANE3+     | Module XAUI Input Lane 3+ [4]                                                                                                                                                                      |

| 65                       |                       | TXLANE3-     | Module XAUI Input Lane 3 [4]                                                                                                                                                                       |

#### Notes:

- Ground connections are common for TX and RX. [1]

- [2] Each connector contact is rated at 0.5A.

- MDIO and MDC timing must comply with IEEE 802.3ae clause 45.3. [3]

- [4] XAUI output characteristics comply with IEEE 802.3ae clause 47.

- Transceivers will be MSA compliant when no signals are present on the vendor specific pins. [5]

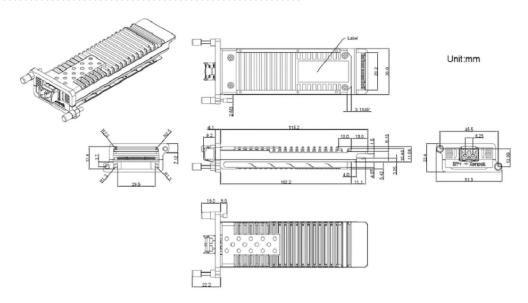

### ,,8,, Mechanical Specifications

#### 8.1. Thermal Management

The transponder is designed for an operation within a case temperature range between 0 to  $+70^{\circ}$ C at an altitude of < 3km. The built in heatsink provides an optimized thermal performance. The user needs to guarantee per system design not to exceed this temperature range. It has to be considered that in case of usage of multiple modules on a single hostboard that there is a temperature rise among the modules hosted side by side. Airflow direction and air speed needs to be choosen accordingly. For further information it is referred to the MSA document.

#### Notice

A-Gear reserves the right to make changes to or discontinue any optical link product or service identified in this publication, without notice, in order to improve design and/or performance. Applications that are described herein for any of the optical link products are for illusrative purposes only. A-Gear makes no representation or warranty that such applications will be suitable for the specified use without further tesing or modification.